BAB V

Rangkaian multiplexer,Decoder,Flip-flop,dan Counter

1.Rangkaian multiplexer, dan Decoder

A.Multiplexer

Fungsi multiplexer adalah memilih 1 dan N (sumber) data masukan dan meneruskan

data yang dipilih itu kepada suatu saluran informasi tunggal. Di dalam multiplexer hanya

terdapat satu jalan masuk dan mengeluarkan data-data yang masuk kepada salah satu

dan N saluran keluar, maka suatu multiplexer sebenamya melaksanakan proses

kebalikan dari demultiplexer. Gambar berikut merupakan suatu multiplexer 4 ke 1

saluran. Perhatikan bahwa konfigurasi pendekodean yang sama digunakan, baik dalam

multiplexer maupun dalam demultiplexer.

B. Demultiplexer

Demultiplexer adalah suatu sistem yang menyalurkan sinyal biner (data serial) pada

salah satu dari n (saluran) yang tersedia, Suatu pendekode dapat diubah menjadi

demultiplexer.

C. Decoder

Decoder berfungsi untuk mengidentifikasi atau mengenali suatu kode tertentu.

Dalam suatu sistem digital perintah-perintah ataupun bilangan-bilangan dikirim dengan

deretan denyut (pulsa) atau tingkatan-tingkatan biner. Misalnya, jika kita menyediakan

karakter 4 bit untukpengiriman instruksi, maka jumlah instruksi berbeda yang dapat

dibuat adalah 24

=16. lnformasi ini diberi kode atau sandi biner. Di pihak lain, seringkali

timbul kebutuhan akan suatu sakelarmultiposisi yang dapat dioperasikan sesuai dengan

kode tersebut. Dengan kata lain, untuk masing-masing dan 16 saluran hanya 1 saluran

yang penambahan pada setiap saat.

Proses untuk identifikasi suatu kode tertentu ini disebut pendekodean atau decoding.

Sistem BCD (Binary Coded Decimal) menerjemahkan bilangan—bilangan desimal

dengan menggantikan setiap digit desimal menjadi 4 bit biner. 4 digit biner dapat dibuat

16 kombinasi, maka 10 di antaranya dapat digunakan untuk menyatakan digit desimal 0

sampai 9. Dengan ini kita memiliki pilihan kode BCD yang luas. Salah satu pilihan yang

disebut kode 8421. Contohnya, bilangan desimal 264 memerlukan 3 gugus yang masingmasing terdiri dari 4 bit biner yang berturut-turut dari khi (MSB) ke kanan (ISB) sebagai

berikut: 0010 0110 0100 (BCD).

Perhatikan gambar, keluaran gerbang AND 1 jika masukan BCD adaLah 0101 dan

sama dengan untuk instruksi masukan yang lain. Karena kode ini merupakan

representasi bilangan desimal 5 maka keluaran ini dinamakan saluran atau jalur 5.

Keluaran decoder ini harus dihubungkan dengan peralatan yang dapat dibaca dan

dimengerti manusia.

Jenis-Jenis Rangkaian Decoder

1) BCD ke 7segment Decoder

Kombinasi masukan biner dan jalan masukan akan diterjemahkan oleh decoder

sehinggamembentuk kombinasi nyala LED peraga (7 segment LED) sesuai dengan

kombinasi masukan biner tersebut. Sebagai contoh, jika masukan biner DCBA = 0001,

maka decoder akan memilih jalur keluaran mana yang akan diaktifkan. Dalam hal ini saluran b dan c diaktifkan sehingga lampu LED b dan C menyala dan menandakan

angka 1.

2) Decoder BCD ke Desimal

Keluarannya dihubungkan dengan tabung indicator angka sehingga kombinasi

angka biner akan menghidupkan lampu indikator angka yang sesuai. Contohnya, D = C

= B =0, A= 1, akan menghidupkan lampu indikator angka 1. Lampu indikator yang

menyala akan sesuai dengan angka biner dalam jalan masuk.

D. Encoder

Encoder adalah kebalikan dari proses decoder di mana suatu pengkode atau

encoder memiliki sejumlah masukan. Pada saat tertentu hanya salah satu dan masukanmasukan itu yang berada pada keluaran 1 dan sebagai akibatnya suatu kode N bit akan

dihasilkan sesuaidengan masukan khusus yang ditambahkan. Misalnya, kita ingin

menyalurkan suatu kode biner untuk setiappenekanan tombol pada keyboard alpha

numeric (suatu mesin tik atau tele type). Pada keyboard tersebut terdapat26 huruf kecil,

10 angka dan sekitar 22 huruf khusussehingga kode yang diperlukan lebih kurang

berjumlah 84. Syarat ini bisa dipenuhi dengan jumlah bit minimum

sebanyak 7 (2=128), Kini misalkan bahwa keyboard D C Btersebut diubah sehingga

setiap saat suatu tombol ditekan, sakelar yang bersangkutan akan menutup. Dandengandemikian menghubungkan suatu catu daya 5 voIt (bersesuaian dengan keadaan1)

dengan saluran masuk tertentu. Diagram skema rangkaian encoder ditunjukkan pada

Encoder merupakan rangkaian penyandi dari bilangan dasar (desimal) menjadi kode

biner(BCD). Bila tombol 1 ditekan, maka D1 akan on menghubungkan jalur A ke logika 0

(GND),akibatnya pada NOT gate 1 timbul keluaran 1 sehingga timbul kombinasi logika

biner 0001, dan seterusnya.

Rangkaian encoder juga dapat disusun dengan menggunakan gerbang NAND

sebagai berikut.

2.Flip-flop

Flip-flop adalah keluarga Multivibrator yang mempunyai dua keadaaan stabil atau

disebutBis table Multivibrator. Rangkaian flip-flop mempunyai sifat sekuensial karena sistem

kerjanya diatur dengan jam atau pulsa. Dengan kata lain, sistem-sistem tersebut bekerja

secara sinkron dengan deretan denyut (pulsa) berperiode T yang disebut jam sistem

(system clock atau disingkat menjadi CLK) seperti yang ditunjukkan dalam Gambar

Berbeda dengan uraian materi sebelumnya yang bekerja atas dasar gerbang logika

dan logikakombinasi, keluarannya pada saat tertentu hanya bergantung pada nilai-nilai

masukan pada saat yang sama. Sistem seperti ini dinamakan tidak memiliki memori. Selain

itu, sistem tersebut menghafal hubungan fungsional antara variabel keluaran dan variabel

masukan.

Fungsi rangkaian flip-flop yang utama adalah sebagai memori (menyimpan

informasi) 1 bit atausuatu sel penyimpan 1 bit. Flip-flop juga dapat digunakan pada

Rangkaian Shift Register, rangkaian Counter, dan lain sebagainya.

Macam-macam flip-flop:

1) RS Flip-Flop

2) J-K Flip-Flop

3) D Flip-Flop

4) CR5 Flip-Flop

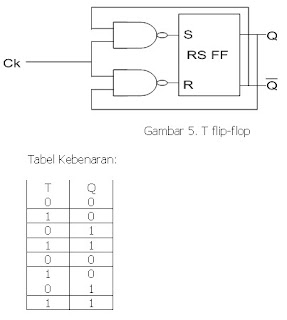

5) T Flip-Flop

A. RS Flip-Flop

RS Flip-Flop adalah rangkaian flip-flop yang mempunyai 2 jalan keluaran (Q).

Simbol-simbolyang ada Pada jalan keluar selalu berlawanan satu dengan yang lain. RSFF adalah flip-flop dasar yang memiliki dua masukan, yaitu R (Reset) dan S (Set). Bila S

diberi logika 1 dan R diberi logika 0, maka output Q akan berada pada logika 0 dan Q

pada logika 1. Bila R diberi logika 1 dan S diberi logika 0, maka keadaan output akan

berubah menjadi Q berada pada logika 1 dan Qnot pada logika 0.

Sifat paling penting dari flip-flop adalah sistem ini dapat menempati salah satu

dari dua keadaanstabil, yaitu stabil I diperoleh saat Q = 1 dan Q01 = O, stabil ke Il

diperoleh saat Q = O dan Q, = 1 yang diperlihatkan pada Gambar

Tabel kebenaran:

Yang dimaksud dengan kondisi terlarang adalah keadaaan yang tidak

diperbolehkan, yaitukondisi output Q sama dengan Q pada saat S = 0 dan R = 0. Yang

dimaksud dengan kondisimemori adalah saat S = 1 dan R = 1, output Q dan Q akan

menghasilkan perbedaan, yaitu jikaQ = 0 maka Q = 1 atau sebaliknya jika Q = 1 maka Q

= 0.

B. J-K Flip-Flop

JK flip-flop sering disebut dengan JK FF atauMaster Slave JK FF karena terdiri

dari dua buah flip- flop, yaitu Master FF dan Slave FE Master Slave JK FF ini memiliki 3

buah terminal input, yaitu J, K, JK i+ Q dan Clock. IC yang dipakai untuk menyusun JK

FF adalah upe 7473 yang mempunyal 2 buah JR flip-flop di mana lay outnya dapat dilihat

pada Vodemaccum IC (Data book 1C). Kelebihan JK FF terhadap FF sebelumnya yaitu

JK FF tidak mempunyai kondisi terlarang artinya berapa pun input yang diberikan asal

ada jam sistem maka akan terjadi perubahan pada output.

C. D Flip-Flop

D flip-flop adalah RS flip-flop yang ditambah dengan suatu inventer pada reset

inputnya. Sifat dan D flip-flop adalah bila input D (Data) dan denyut jam sistem (pulse

clock) bemilal 1, maka output Q akan bernilai 1 dan bila input D bernilai 0, maka D flipflop akan berada pada keadaanreset atau output Q hemilai 0.

D. CRS Flip- Flop

CR5 flip-flop adalah clocked RS-FF yang dilengkapi dengan sebuah terminal

denyut jam sistem.Denyut Jam sistem ini berfungsi mengatur keadaan Set dan Reset.

Bila denyut jam sistem bernilai 0,maka perubahan nilai pada input R dan S tidak akan

mengakibatkan perubahan pada output Q dan Qnot. Akan tetapi, apabila denyut jam istem

bernilai 1, maka perubahan pada input R dan S dapat mengakibatkan perubahan pada

output Q dan Qnot.

E. T Flip-Flop

Rangkaian T flip-flop atau Toggle flip-flop (TFF) dapat dibentuk dari modifikasi

clocked RSFF,DFF maupun JKFE TFF mempunyai sebuah terminal input T dan dua

buah terminal output Qdan Qnot. TFF banyak digunakan pada rangkaian Counter,

pembagi frekuensi dan sebagainya.

3.Register

Register adalah sekelompok flip-flop yang dapat dipakai untuk menyimpan dan

untuk mengolahinformasi dalam bentuk linier.

Ada 2 jenis utama Register yaitu:

1. Storage Register (register penyimpan)

2. Shift Register (register geser)

Register penyimpan digunakan apabila kita hendak menyimpan informasi untuk

sementara,sebelum informasi itu dibawa ke tempat lain. Banyaknya kata/bit yang dapat

disimpan, bergantungpada banyaknya flip-flop dalam register.Satu flip-flop dapat

menyimpan satu bit. Bila kita hendak menyimpan informasi 4 bit makakita butuhkan 4 flipflop.

Shift Register adalah suatu register yang informasinya dapat bergeser (digeserkan). Dalam

register geser flip-flop salingg terhubung, sehingga isinya dapat digeserkan dan satu flipflop ke flip-flop yang lain, ke kiri atau ke kanan atas perintah denyut jam sistem.

Dalam aat ukur digital, register dipakai untuk mengingat data yang sedang ditampilkan.

Ada 4 Shift Register yaitu sebagai berikut.

A. Register Geser SISO

Informasi/data dimasukkan melalui word ini dan akan dikeluarkan jika ada denyut

jam sistemberlalu dari 1 ke 0. Karena jalan keluarnya flip-flop satu dihubungkan kepada

jalan masukflip-flop berikutnya, maka informasi di dalam register akan digeser ke kanan

atas perintah daridenyut jam sistem.

Register geser SiSO ada 3 macam yaitu:

a. Shift Right Register (SRR) Register geser kanan

b. Shift Left Register (SLR) Register geser kiri

c. Shift Control Register dapat berfungsi sebagai SSR maupun SlR

Rangkaian Shift control adalah seperti gambar di bawah.

Rangkaian ini untuk mengaktifkan geserKanan/kiri yang ditentukan oleh SC.

Jika SC=1, maka akan mengaktifkan SLR.

JikaSC=0, maka akan mengaktifkan SRR.

B. Register Geser SIPO

Ini adalah register geser dengan masukan data secara serial dan keluaran data

secara paralel. Gambar rangkaiannya adalah sebagai berikut (SIPO menggunakan D-FF).

Cara kerja:

Masukan-masukan data secara deret akan dikeluarkan oleh D-FF setelah masukan

denyut jamsistem dan 0 ke 1. Keluaran data/informasi serial akan dapat dibaca secara

paralel setelahdiberikan satu komando (Read Out). Bila di jalan masuk Read Out diberi nilai

0, maka semuakeluaran AND adalah 0 dan bila Read Out diberi nilai 1, maka pintu-pintu

AND menghubungIangsungkan sinyal-sinyal yang ada di Q masing-masing flip-flop.

C. Register Geser PIPO

Ini adalah register geser dengan masukan data secara jajar/paralel dan keluaran

jajar/paralel.

Gambar rangkaiannya adalah sebagai herikut (PIPO menggunakan D-FF).

\

Cara kerja:

Sebelum dimasuki data rangkaìan direset dulu agar keluaran Q semuanya 0.

Setelah itu datadimasukkan secara paralel pada input D-N dan data akan diloloskan keluar

secara parallel setelah flip-flop mendapat denyut jam sistem dari 0 ke 1.

D. Register Geser PISO

Ini adalah register geser dengan masukan data secara paralel dan dikeluarkan secara

deret/serial.Gambar rangkaian register PISO menggunakau D-FF adalah sebagai

berikut.

Rangkaian di atas merupakan register geser dengan panjang kata 4 bit. Semua

jalan masukjam sistem dthubungkan jajar. Data-data yang ada di A, B, C, D dimasukkan

ke flip-flop secaraserempak, apabila di jalan masuk Data l.oad diberi nilai 1.

Cara Kerja:

a. Mula-mula jalan masuk Data Ioad = O, maka semua pintu NAND mengeluarkan 1 ,

sehingga jalanmasuk set dan reset semuanya 1 berarti bahwa jalan masuk set dan

reset tidak berpengaruh.

b. Jika Data Load = 1, maka semua input paralel akan dilewatkan oleh NAND. Misal

jalan masukA = 1, maka pmtu NAND 1 mengeluarkan O adapun pintu NAND 2

mengeluarkan 1. Dengandemikian flip-flop diset sehingga menjadi Q = 1. Karena

flip-flop yang lain pun dihubungkandengan cara yang sama, maka mereka juga

Sistem Komputer SMK/MAK Kelas X Semester I 127

mengoper informasi pada saat Data Load diberi nilai 1. Setelah informasi berada di

dalam register, Data Load diberi nilai 0. Informasi akan dapatdikeluarkan dan

register dengan cara memasukkan denyut jam sistem dengan denyut demidenyut

keluar deret/seri. Untuk keperluan ini jalan masuk D dihubungkan kepada

keluaranQ.

4.Counter

Counter (pencacah) adalah

alat/rangkaian digital yang berfungsi menghitung/mencacah banyaknyadenyut jam sistem

atau juga berfungsi sebagai pembagi frekuensi, pembangkit kode biner, Gray.

Ada 2 jenis pencacah yaitu sebagai berikut.

1. Pencacah sinkron (synchronous counters) atau pencacah jajar.

2. Pencacah tak sinkron (asynchronous counters) yang kadang-kadang disebut juga

pencacah deret (series counters) atau pencacah kerut (ripple counters).

Counter juga disebut pencacah atau penghitung yaitu rangkaian logika sekuensial

yang digunakan untuk menghitung jumlah pulsa yang diberikan pada bagian

masukan. Counter digunakan untuk berbagai operasi aritmatika, pembagi frekuensi,

penghitung jarak (odometer), penghitung kecepatan (spedometer), yang pengembangannya digunakan luas dalam aplikasi perhitungan pada instrumen ilmiah,

kontrol industri, komputer, perlengkapan komunikasi, dan sebagainya .

Counter tersusun atas sederetan flip-flop yang dimanipulasi sedemikian rupa dengan

menggunakan peta Karnough sehingga pulsa yang masuk dapat dihitung sesuai

rancangan. Dalam perancangannya counter dapat tersusun atas semua jenis flip-flop,

tergantung karakteristik masing-masing flip-flop tersebut.

Dilihat dari arah cacahan, rangkaian pencacah dibedakan atas pencacah naik (Up

Counter) dan pencacah turun (Down Counter). Pencacah naik melakukan cacahan dari

kecil ke arah besar, kemudian kembali ke cacahan awal secara otomatis. Pada pencacah

menurun, pencacahan dari besar ke arah kecil hingga cacahan terakhir kemudian kembali

ke cacahan awal.

Tiga faktor yang harus diperhatikan untuk membangun pencacah naik atau turun yaitu

(1) pada transisi mana Flip-flop tersebut aktif. Transisi pulsa dari positif ke negatif atau

sebaliknya, (2) output Flip-flop yang diumpankan ke Flip-flop berikutnya diambilkan dari

mana. Dari output Q atau Q, (3) indikator hasil cacahan dinyatakan sebagai output yang

mana. Output Q atau Q. ketiga faktor tersebut di atas dapat dinyatakan dalam persamaan

EX-OR.

Secara global counter terbagi atas 2 jenis, yaitu: Syncronus Counter dan Asyncronous

counter. Perbedaan kedua jenis counter ini adalah pada pemicuannya. Pada

Syncronous counter pemicuan flip-flop dilakukan serentak (dipicu oleh satu sumber clock)

susunan flip-flopnya paralel. Sedangkan pada Asyncronous counter, minimal ada salah

satu flip-flop yang clock-nya dipicu oleh keluaran flip-flop lain atau dari sumber clock lain,

dan susunan flip-flopnya seri. Dengan memanipulasi koneksi flip-flop berdasarkan peta

karnough atau timing diagram dapat dihasilkancounter acak, shift counter (counter sebagai

fungsi register) atau juga up-down counter.

A. Synchronous Counter

Syncronous counter memiliki pemicuan dari sumber clock yang sama dan susunan

flip-flopnya adalah paralel. Dalam Syncronous counter ini sendiri terdapat perbedaan

penempatan atau manipulasi gerbang dasarnya yang menyebabkan perbadaan waktu

tunda yang di sebut carry propagation delay.Penerapan counter dalam aplikasinya adalah

berupa chip IC baik IC TTL, maupun CMOS, antara lain adalah: (TTL) 7490, 7493, 74190,

74191, 74192, 74193, (CMOS) 4017,4029,4042,dan lain-lain.

Pada Counter Sinkron, sumber clock diberikan pada masing-masing input Clock dari

Flip-flop penyusunnya, sehingga apabila ada perubahan pulsa dari sumber, maka

perubahan tersebut akan men-trigger seluruh Flip-flop secara bersama-sama.

Rangkaian Down Counter Sinkron 3 bit

Rangkaian Up/Down Counter Sinkron

Rangkaian Up/Down Counter merupakan gabungan dari Up Counter dan Down

Counter. Rangkaian ini dapat menghitung bergantian antara Up dan Down karena adanya

input eksternal sebagai control yang menentukan saat menghitung Up atau Down. Pada

gambar 4.4 ditunjukkan rangkaian Up/Down Counter Sinkron 3 bit. Jika input CNTRL

bernilai ‗1‘ maka Counter akan menghitung naik (UP), sedangkan jika input CNTRL

bernilai ‗0‘, Counter akan menghitung turun (DOWN).

Rangkaian Up/Down Counter Sinkron 3 bit

B. Asyncronous counter

Seperti tersebut pada bagian sebelumnya Asyncronous counter tersusun atas flip-flop

yang dihubungkan seri dan pemicuannya tergantung dari flip-flop sebelumnya, kemudian

menjalar sampai flip-flop MSB-nya. Karena itulah Asyncronous counter sering disebut juga

sebagai ripple-through counter.

Sebuah Counter Asinkron (Ripple) terdiri atas sederetan Flip-flop yang

dikonfigurasikan dengan menyambung outputnya dari yan satu ke yang lain. Yang

berikutnya sebuah sinyal yang terpasang pada input Clock FF pertama akan mengubah

kedudukan outpunyanya apabila tebing (Edge) yang benar yang diperlukan terdeteksi.

Output ini kemudian mentrigger inputclock berikutnya ketika terjadi tebing yang

seharusnya sampai. Dengan cara ini sebuah sinyal pada inputnya akan meriplle

(mentrigger input berikutnya) dari satu FF ke yang berikutnya sehingga sinyal itu mencapau ujung akhir deretan itu. Ingatlah bahwa FF T dapat membagi sinyal input

dengan faktor 2 (dua). Jadi Counter dapat menghitung dari 0 sampai 2‖ = 1 (dengan n

sama dengan banyaknya Flip-flop dalam deretan itu).

Rangkaian Up Counter Asinkron 3 bit

Timing Diagram untuk Up Counter Asinkron 3 bit

Berdasarkan bentuk timing diagram di atas, output dari flip-flop C menjadi clock dari

flip-flop B, sedangkan output dari flip-flop B menjadi clock dari flip-flop A. Perubahan pada

negatif edge di masing-masing clock flip-flop sebelumnya menyebabkan flip-flop

sesudahnya berganti kondisi (toggle), sehingga input-input J dan K di masing-masing flipflop diberi nilai ‖1‖ (sifat toggle dari JK flip-flop).

C. Counter Asinkron Mod-N

Counter Mod-N adalah Counter yang tidak 2n

. Misalkan Counter Mod-6, menghitung :

0, 1, 2, 3, 4, 5. Sehingga Up Counter Mod-N akan menghitung 0 s/d N-1, sedangkan Down

Counter MOD-N akan menghitung dari bilangan tertinggi sebanyak N kali ke bawah.

Misalkan Down Counter MOD-9, akan menghitung : 15, 14, 13, 12, 11, 10, 9, 8, 7, 15, 14,

13,..

Rangkaian Up Counter Asinkron Mod-6

Sebuah Up Counter Asinkron Mod-6, akan menghitung : 0,1,2,3,4,5,0,1,2,… Maka

nilai yang tidak pernah dikeluarkan adalah 6. Jika hitungan menginjak ke-6, maka counter

akan reset kembali ke 0. Untuk itu masing-masing Flip-flop perlu di-reset ke nilai ‖0‖

dengan memanfaatkan input-input Asinkron-nya( dan

dan ). Nilai ‖0‖ yang akan

dimasukkan di PC didapatkan dengan me-NAND kan input A dan B (ABC =110 untuk

desimal 6). Jika input A dan B keduanya bernilai 1, maka seluruh flip-flop akan di-reset.

). Nilai ‖0‖ yang akan

dimasukkan di PC didapatkan dengan me-NAND kan input A dan B (ABC =110 untuk

desimal 6). Jika input A dan B keduanya bernilai 1, maka seluruh flip-flop akan di-reset.

dan

dan ). Nilai ‖0‖ yang akan

dimasukkan di PC didapatkan dengan me-NAND kan input A dan B (ABC =110 untuk

desimal 6). Jika input A dan B keduanya bernilai 1, maka seluruh flip-flop akan di-reset.

). Nilai ‖0‖ yang akan

dimasukkan di PC didapatkan dengan me-NAND kan input A dan B (ABC =110 untuk

desimal 6). Jika input A dan B keduanya bernilai 1, maka seluruh flip-flop akan di-reset.

Rangkaian Up/Down Counter Asinkron 3 bit

Rangkaian Up/Down Counter merupakan gabungan dari Up Counter dan Down

Counter. Rangkaian ini dapat menghitung bergantian antara Up dan Down karena adanya

input eksternal sebagai control yang menentukan saat menghitung Up atau Down. Pada

rangkaian Up/Down Counter ASinkron, output dari flip-flop sebelumnya menjadi input clock

dari flip-flop berikutnya.

D. Perancangan Counter

Perancangan counter dapat dibagi menjadi 2, yaitu dengan menggunakan peta

Karnough, dan dengan diagram waktu. Berikut ini akan dijelaskan langkah-langkah dalam

merancang suatu counter.

a). Perancangan Counter Menggunakan Peta Karnaugh

Umumnya perancangan dengan peta karnaugh ini digunakan dalam merancang

syncronous counter. Langkah-langkah perancangannya:

a. Dengan mengetahui urutan keluaran counter yang akan dirancang, kita tentukan

masukan masing-masing flip-flop untuk setiap kondisi keluaran, dengan

menggunakan tabel kebalikan.

b. Cari fungsi boolean masing-masing masukan flip-flop dengan menggunakan peta

Karnough. Usahakan untuk mendapatkan fungsi yang sesederhana mungkin, agar

rangkaian counter menjadi sederhana.

c. Buat rangkaian counter, dengan fungsi masukan flip-flop yang telah ditentukan.

Pada umumnya digunakan gerbang-gerbang logika untuk membentuk fungsi

tersebut.

b). Perancangan Counter Menggunakan Diagram Waktu

Umumnya perancangan dengan diagram waktu digunakan dalam merancang

asyncronous counter, karena kita dapat mengamati dan menentukan sumber pemicuan

suatu flip-flop dari flip-flop lainnya. Adapun langkah-langkah perancangannya:

a. Menggambarkan diagram waktu clock, tentukan jenis pemicuan yang digunakan,

dan keluaran masing-masing flip-flop yang kita inginkan. Untuk n kondisi keluaran,

terdapat njumlah pulsa clock.

b. Dengan melihat keluaran masing-masing flip-flop sebelum dan sesudah clock aktif

(Qn dan Qn+1), tentukan fungsi masukan flip-flop dengan menggunakan tabel

kebalikan.

c. Menggambarkan fungsi masukan tersebut pada diagram waktu yang sama.

d. Sederhanakan fungsi masukan yang telah diperoleh sebelumnya, dengan melihat

kondisi logika dan kondisi keluaran flip-flop. Untuk flip-flop R-S dan J-K

kondisi don’t care (x) dapat dianggap sama dengan 0 atau 1.

e. Tentukan (minimal satu) flip-flop yang dipicu oleh keluaran flip-flop lain. Hal ini

dapat dilakukan dengan mengamati perubahan keluaran suatu flip-flop setiap

perubahan keluaran flip-flop lain, sesuai dengan jenis pemicuannya.

f. Buat rangkaian counter, dengan fungsi masukan flip-flop yang telah ditentukan.

Pada umumnya digunakan gerbang-gerbang logika untuk membentuk fungsi

tersebut. (Hamacher, Vranesic, & Zaky, Organisasi Komputer, 2004, hal. 571)

BAB V materi sistem komputer

4/

5

Oleh

Tanya

EmoticonEmoticon